# Komfortabler Personalcomputer für den erfahrenen Amateur (3)

Dipl.-Ing. A. MUGLER - Y27NN, Dipl.-Ing. H. MATHES

Damit ist über die Verstärkerstufe (VT1) der Anschluß einer Hörkapsel und die Ausgabe von Tönen möglich. Weiterhin kann dieser Tonausgang als Mithörkontrolle für das Kassettenmagnetbandgerät genutzt werden.

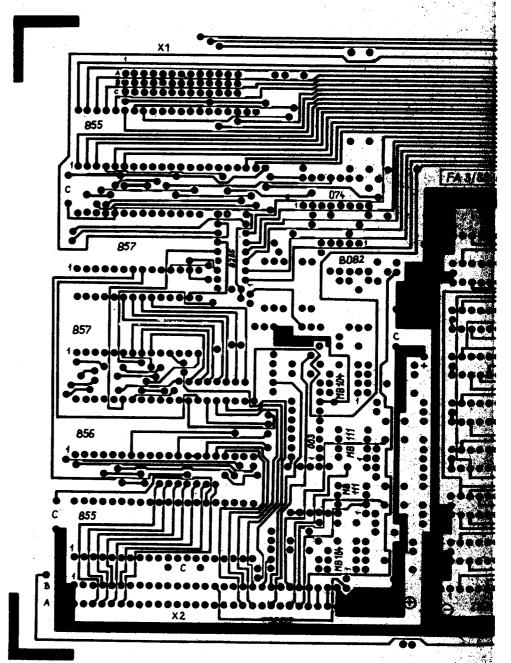

Auf Adresse 84H folgt als zweiter Baustein die System-PIO (D56). Diese PIO U 855 D dient dem parallelen Datenaustausch zwischen CPU und Peripherie. Sie verfügt über zwei Ports zu je 8 Bit, die man wahlweise als Eingang bzw. Ausgang programmieren kann. In diesem Fall realisiert sie die Schnittstellen zur Tastatur und zum Kassettenmagnetbandgerät. Sechs LED, die sich auf der Tastatur befinden, zeigen bestimmte Zustände des Computers an (Bild 31). An den An-

schlüssen A0 bis A7 (PIO-Port A) wird die Tastatur mit den Leitungen TD0 bis TD6 und TAST angeschlossen. B0 bis B5 steuern LED0 bis LED5, B6 und B7 von Port B dienen dem Kassettenmagnetbandgerät als Aus- bzw. Eingang. Die gesamte Belegung der System-PIO-Ports ist aus Bild 31 ersichtlich [3].

#### 2.2.3. Anwender-CTC, Anwender-PIO

Die Kanaladressen 8CH bis 8FH belegen die Anwender-CTC (D58) mit den Kanälen 0 bis 3, wobei nur die Kanäle 0, 1 und 2 Ein- und Ausgänge besitzen. Dem Kanal 3 steht nur ein Eingang zur Verfügung. Die Eingänge TRG0 bis TRG3 sowie die Ausgänge TO0, TO1 und TO2 wurden auf den Koppelbus geführt und stehen dem Anwender frei zur Verfügung. Eine eventuelle Kaskadierung mehrerer Kanäle, z. B. bei Uhrenbetrieb, muß über den Koppelsteckverbinder X2 realisiert werden. Es existiert dazu kein separates Koppelfeld.

Den zweiten Anwenderbaustein stellt die PIO D59 (90H bis 93H) dar. Mit ihr lassen sich parallele Schnittstellen realisieren. Es können an den Ports A und B die verschiedensten Ein- und Ausgabegruppen (Digital/Analog-Wandler, Tongeneratoren, Schalter, Taster, Anzeigeelemente, Treiberstufen für Leistungsausgabe, Drucker usw.) angeschlossen werden. Ausgang IEO (auf Systembus X3 geführt) dient der weiteren Einbindung von peripheren Bausteinen niedrigerer Priorität über deren IEI- und IEO-Anschluß in die "Daisy Chain" [3].

## 2.2.4. Anwender-SIO, V24- bzw. IFSS-Interface

Will man Daten über eine größere Entfernung übertragen, so ist es vorteilhaft, wenn das über wenige Leitungen geschieht. Da für den Datenaustausch bei 8-Bit-Computern 1 Byte üblich ist, muß dieses Byte in ein serielles Format gewandelt werden.

Zur Realisierung serieller Schnittstellen (Anschluß Floppy-Controller, Drucker und anderer seriell ansteuerbarer Baugruppen) befindet sich auf der zentralen Platine eine SIO U 856 D (D57). Die beiden Taktsignale /RxCA und /RxCB entstehen, wie bereits beschrieben, in der System-CTC (D55). Um neben der IFSS-Schnittstelle eine V.24-Schnittstelle (auch RS 232 C möglich) realisieren zu können, werden die Signale /RTSA, /RTSB, /DTRA und /DTRB auf den Koppelbus geführt.

Da über Leitungen mit normalem TTL-Pegel nur einige hundert Millimeter störungsfrei überbrückt werden können, muß man mit größeren Spannungshüben oder einem eingeprägten Strom arbeiten. Eine Schnittstelle mit Spannungspegeln ist die V.24-Schnittstelle, bei der mit z.B.

-12 V und +12 V übertragen wird. Als Stromschnittstelle findet die 20-mA-Stromschleife Verwendung. So lassen sich Entfernungen von über 100 m überbrücken, wobei die Entfernung noch abhängig vom der Übertragungsgeschwindigkeit ist.

Als IFSS-Schnittstelle wurden für die Kanäle A und B 20-mA-Stromschleifen (Sender und Empfänger) realisiert. Über die Optokoppler A2 bis A5 erfolgt die galvanische Trennung zwischen Gerät und Übertragungsleitung. Sowohl Sender als auch Empfänger können aktiv, also mit Stromeinspeisung, oder passiv arbeiten. Die Stromquellen werden durch Widerstände gebildet. Die Auswahl der Betriebsart (aktiv/passiv) kann mittels Brükken im Koppelfeld auf der zentralen Platine erfolgen. Über diese Schnittstellen läßt sich der Computer auch an ein lokales Netz (z. B. Ringnetz) anschließen. Die Leitungen TxDA2, RxDA1 und RxDA2 sind auf einen IFSS-Anschluß geführt [2].

#### 2.2.5. Kassetteninterface

Da nach dem Abschalten des Personalcomputers der Informationsinhalt der dynamischen Speicher verloren geht und auch der vorhandene Speicherplatz begrenzt ist, müssen Daten und Programme auf einem nichtflüchtigen Speicher, z. B. Kassettenmagnetband, abgelegt werden.

Für die Ansteuerung des KMBG wurde auf der zentralen Platine im LOAD-Zweig ein Bandpaß mit nachfolgendem Trigger mittels Doppel-OPV B 082 D (A1) aufgebaut, um das vom KMBG kommende Signal für die als Eingang programmierte Leitung B7 der System-PIO (D56) aufzubereiten. Die beiden Dioden dienen dabei zur Spannungsbegrenzung. Im SAVE-Zweig befindet sich ein passiver Spannungsteiler zur Anpassung an die Eingangsstufe des KMBG. Die Pegel im LOAD- bzw. SAVE-Zweig können mit den Einstellreglern R1 und R2 angepaßt werden.

Die Beschreibung des im Mustergerät integrierten KMBG und der dazu noch notwendigen Hardware erfolgt im Abschnitt 3.3.

#### 3. Die Peripherie

### 3.1. Bildschirmansteuerung (BSA)

Zur Kommunikation zwischen Mensch und Computer besitzt neben der Tastatur die BSA eine große Bedeutung. Um den Dialog visuell zu unterstützen, hat sich der Bildschirm in den verschiedensten Varianten (LCD-Display, Farbmonitor, Grafikdisplay usw.) durchgesetzt. Er dient der momentanen Darstellung von Informationen. Als Monitor für den Heimgebrauch ist der Einsatz eines handelsüblichen Fernsehgerätes möglich.

Neben der Einbeziehung der CPU (geringer Bauelementeaufwand) ist die separate Realisierung der BSA vorteilhaft. Es ergibt sich somit die Austauschbarkeit der BSA gegen andere Bildschirmansteuerungen (z.B. 80 × 24-Zeichen-BSA oder Grafikmodul). Das vom Fernsehen bekannte Darstellungsprinzip beruht auf der Helligkeitssteuerung des Elektronenstrahls. Dieser Strahl überstreicht dabei 625 Zeilen bei einer Frequenz von 15 625 Hz (Zeilendauer 64 µs) bei Anwendung des Zeilensprungverfahrens.

Bei der vorliegenden BSA wurden 312 Zeilen mit einer Bildfolgefrequenz von 50 Hz (ohne Zeilensprung) realisiert.

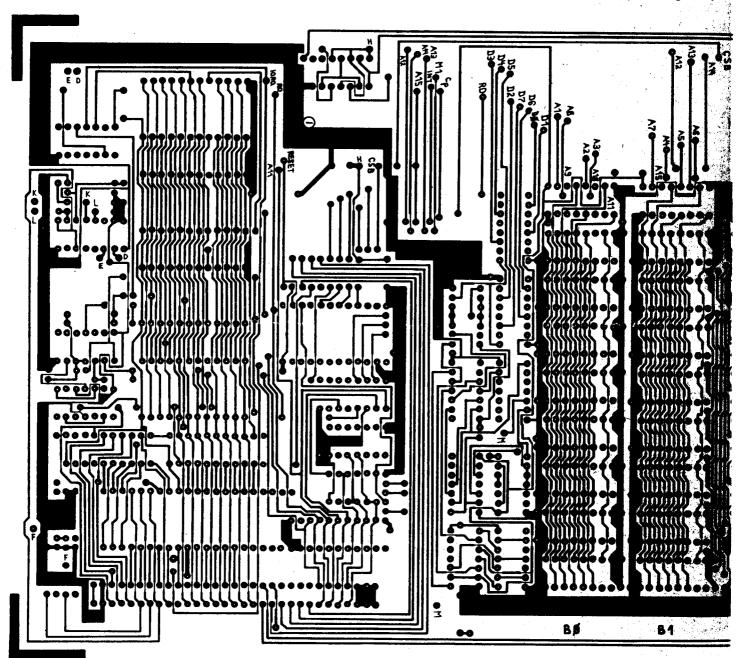

Bild 4a: Leitungsführung der Bestückungsseite der zentralen Platine des Personalcomputers

Das ermöglicht die Darstellung von 32 Zeichenzeilen zu je 8 Fernsehzeilen. Außerdem dienen sieben dunkelgetastete Zeichenzeilen der Darstellung des oberen (3 Zeichenzeilen) sowie des unteren Bildrandes (4 Zeichenzeilen). Jede Zeichenzeile besteht aus 64 Zeichen zur Informationsdarstellung und 32 dunkelgetasteten Zeichen zur linken und rechten Bildranddarstellung (je 16 Zeichenpositionen). Im Normalfall werden zur Darstellung alphanumerischer Zeichen nur 16 Zeichenzeilen angesprochen, jede zweite Zeile bleibt dunkel, läßt sich jedoch bei der Arbeit mit der möglichen Pseudografik nutzen. Es sind also 1024 bzw. bei Pseudografik 2048 Zeichen je Bild darstellbar. Ein Zeichen besteht dabei aus einer 8 × 7-Punkt-Matrix. Die Adreßbelegung der einzelnen Zeichenpositionen des Bildschirms ist aus Bild 12 ersichtlich.

Da im Gegensatz zu einer "echten" Grafik die Zeichen bei dieser BSA kodiert vorliegen müssen, wird der gesamte Zeichensatz auf EPROM (Zeichengenerator) programmiert. Durch den Einsatz eines U2716D (2 K × 8 Bit) lassen sich 256 unterschiedliche Zeichen darstellen. Um ein Fernsehgerät über dessen Antenneneingang ansteuern zu können, muß die BSA ein moduliertes HF-Signal erzeugen. Dieses enthält neben der Videoinformation die Austast- und Synchronimpulse. Die Austastung von Bildteilen legt den obengenannten Bildrand fest, wodurch keine der darzustellenden Informationen verschluckt bzw. unscharf abgebildet werden.

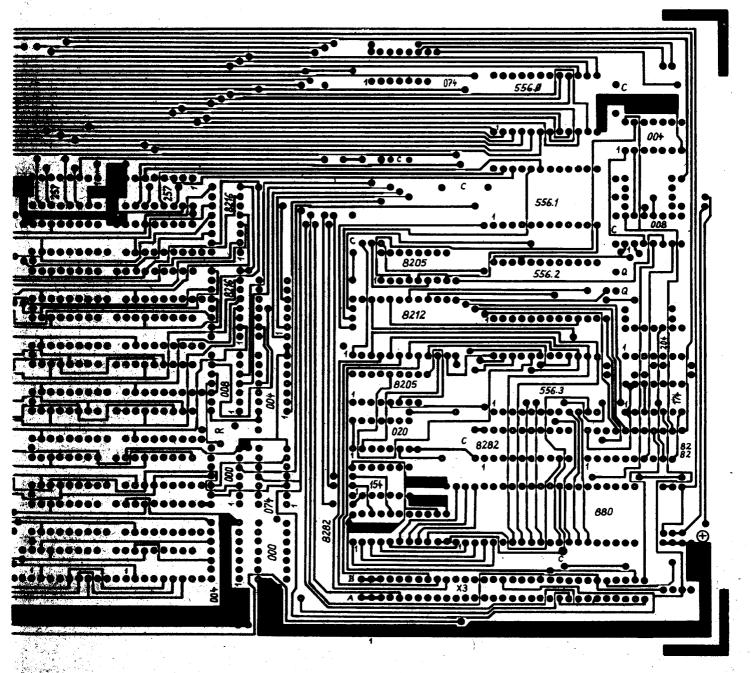

Bild 6 zeigt den Übersichtsplan der gesamten BSA. Über die Adreßdekodierung (D114, D115.1) wird die Anfangsadresse des Bildschirms mit ØF800H festgelegt. Bei /RFSH = Low ist der Zugriff auf die BSA gesperrt. Das Ausgangssignal der Adreßdekodierung schaltet bei Speicherzugriffen (/MREQ aktiv) über den Multiplexer (D104 bis D106) die CPU-Adresse auf die Adreßeingänge A0 bis A10 des Bildwiederholspeichers (BWS). Dieser besteht aus vier U 214 D (D107 bis D110) und verfügt somit über eine Speicherkapazität von 2048 × 8 Bit.

Im BWS wird immer ein komplettes Bild, d. h., die ASCII-Kodierung der auf dem Bildschirm dargestellten Zeichen, abgespeichert. Da der Arbeits-RAM der zentralen Platine 64 KByte umfaßt, arbeiten der BWS und die letzten beiden KByte des aktuellen dRAM-Blockes parallel. Um Buskonflikte zu vermeiden, wird der BWS nur beschrieben; das Lesen erfolgt vom RAM der zentralen Platine. Daher kann man als Datentreiber (D111) die IS

DS 8282 D einsetzen. Eine Datenrichtungsumschaltung ist für die BSA dadurch nicht erforderlich. Greift die CPU nicht auf die BSA zu, liegen die Adressen des Bildwiederholzählers (D123 bis D127) am BWS. Dieser realisiert unter anderem die Bereitstellung der Spaltenund Zeilenadressen bei der zyklischen Bildwiederholung.

Den Bildpunkttakt erzeugt ein Quarzgenerator, der mit einer Frequenz von 10,5 MHz schwingt (D101). Hierbei ist durchaus der Einsatz eines LC-Oszillators möglich [8]. D102 zählt die für eine Zeichenbreite notwendigen 7 Bildpunkte. Für die Darstellung alphanumerischer Zeichen ist der Zeichenzwischenraum im Zeichengenerator programmiert. Nach je 7 Bildpunkten wird der Bildwiederholzähler durch den Zeichentakt um eins weitergeschaltet. D123 und D124 bilden

dabei den Zeichenspaltenzähler, der die insgesamt  $96 \times 66,6$  ns langen Zeichen zählt. Aus den Zählerständen werden die zur Zeichenspaltenadressierung notwendigen 6 Adreßleitungen, der Zeilensynchronimpuls und die Zeichenaustastung erzeugt.

Der sich anschließende Zeichenlinienzähler (D125) zählt die für eine Zeichenreihe notwendigen 8 Fernsehzeilen und erzeugt die Adressen A0 bis A2 für den Zeichengenerator D113. Nach der achten Fernsehzeile einer Zeichenreihe wird der durch die Zähler D126 und D127 gebildete Zeichenreihenzähler um eins weitergeschaltet. An seinen Ausgängen liegen die 5 Adressen (32 Zeichenreihen) für den BWS. Schließlich realisiert eine De-

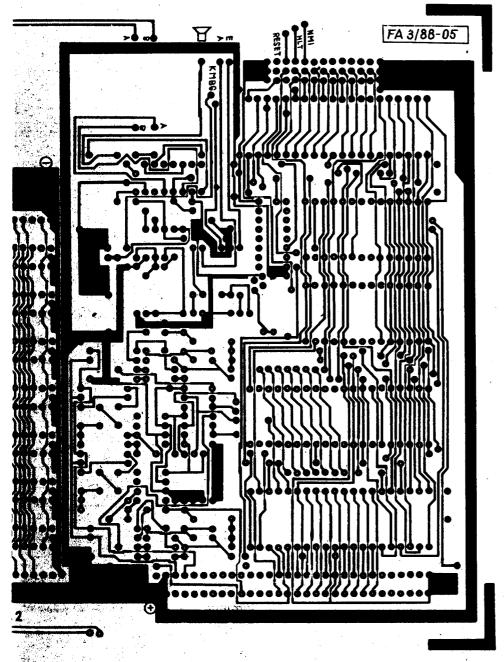

Bild 4b: Leitungsführung der Leiterseite der zentralen Platine des Personalcomputers

kodierung die Austastung der 7 Bildrandzeilen und die Generierung des Bildsynchronimpulses.

Der Zeichentakt wird weiterhin zur Übernahme der vom Zeichengenerator bereitgestellten 7-Bit-Information in den Parallel/Serien-Wandler (Register D119 und D120) benötigt. Zwei Gatter des D103.1 erzeugen zusammen mit einer RC-Kombination (Impulsverkürzung) den zur Übernahme erforderlichen H-Impuls. Nach der Übernahme des Bitmusters in die Register-Schaltkreise D 195 D werden durch den Bildpunkttakt die 7 Bit aus dem Parallel/Serien-Wandler "herausgeschoben". Diese stellen die Videoinformation dar.

Der Zeichengenerator D113 liegt mit seinen Adreßeingängen A3 bis A10 über das durch D112 realisierte Zeichenlatch an den Datenausgängen des BWS. A0 bis A2

liegen an den Ausgängen des Zeichenlinienzählers D125. Im Zeichengenerator ist entsprechend des an A3 bis A10 liegenden ASCII-Kodes das Bitmuster des entsprechenden Zeichens abgespeichert A0, A1 und A2 bezeichnen dabei die aktuelle Fernsehzeile, in der sich der Elektronenstrahl gerade befindet. Die Grafiksymbole und Sonderzeichen sind in Bild 10 dargestellt. Der Zeichensatz ist so aufgebaut, daß die zweite Hälfte die Inversdarstellung der ersten 128 Zeichen realisiert. Dieser Umstand wird zur Darstellung des Kursors mittels Setzen von Bit 7 genutzt. Prinzipiell besteht unter Beachtung von Zeichenaufbau (Bild 11) und Kodierung die Möglichkeit, eine Änderung des vorliegenden Zeichensatzes (z. B. spezielle Pseudografikelemente zur Lösung bestimmter Aufgaben), vorzuneh-(wird fortgesetzt)